# ISL6253EVAL1B Evaluation Board Setup Procedure

### **Application Note**

May 2004

## **General Description**

The ISL6253EVAL1B EV kit includes all the circuitry needed to demonstrate the capabilities of the ISL6253 Lithium-Ion battery-charger with integrated AC adapter current limit. The user can experiment with an extensive matrix of battery charge parameters, AC adapter current limit, monitor functions, and load switching.

The ISL6253 charger IC controls a high efficiency 300kHz fixed-frequency DC/DC synchronous-rectifier buck-converter. The battery charger employs a current-limited voltageclamped regime while simultaneously protecting the system AC adapter power source from an overcurrent event. If the AC adapter output approaches the user selectable current limit, the battery charger output will automatically foldback to the extent that the AC adapter output current remains compliant. Once the demand on the AC adapter subsides, the battery charger output will resume normal operation.

The AC Adapter current limit (ACLIM), battery charger current limit (CHLIM), and output voltage limit (VADJ) are programmed by applying the appropriate voltage relative to the GND pin. Each of these three parameters may be independently programmed by connecting to one of the three built-in settings. The three built-in settings are chosen by connecting ACLIM, CHLIM, and VADJ to either VREF, GND, or floating.

The ISL6253 is capable of controlling two P-CH MOSFET isolation switches SGATE and BGATE, that replace diodes typically used for this purpose. The SGATE pin controls a switch that prevents the battery from back-feeding into the system input power source as is possible when an AC adapter remains connected to the system while de-energized. The BGATE pin controls a switch that provides a low impedance discharge path between the battery and the system power bus when the AC adapter is unavailable; otherwise the switch is open, isolating the battery from the input power source.

The ISL6253 has two general purpose 1.26V voltage comparator inputs DCSET and ACSET, that control open drain outputs DCPRN and ACPRN. The ICM pin provides a 0V to 2V output signal that is proportional to the AC adapter output current.

### **Ordering Information**

| C) PAC                 | PKG.<br>BKAGE DWG. # | TEMP.<br>RANGE (°C) | PART #                 |

|------------------------|----------------------|---------------------|------------------------|

| 28 Ld 5x5<br>(Pb-free) | QFN L28.5x5          | -10 to 100          | ISL6253HRZ<br>(Note 1) |

| (Pb-free)              |                      |                     | (Note 1)               |

NOTE

Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J Std-020B.

- ±0.5% Voltage Accuracy from -10°C to +100°C

- ±3% AC Adapter Current Limit Accuracy

- ±4% Battery Charger Current Limit Accuracy

- · Selectable 2, 3, or 4 Series Cell Battery Packs

- Trickle Charge Mode 10% of Battery Charger Current Limit when Battery Voltage is Less than 3.0V per Cell

- Input Voltage Range 7V to 25V

- · High Efficiency 300kHz Synchronous Buck Rectifier

- · Efficient Light Load Diode Emulation Mode

- 150°C Thermal Shutdown Protection

- · AC Adapter Output Current Monitor

- · AC Adapter Present Indicator

- · DC Adapter Present Indicator

- · Controls P-CH MOSFET Power Source Isolation Switch

- · Controls P-CH MOSFET Battery Isolation Switch

- Pb-free Available

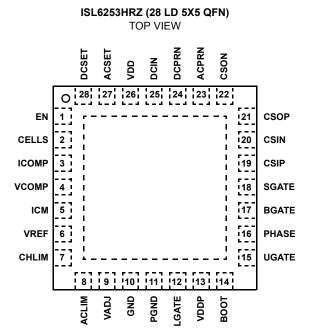

#### Pinout

<sup>2.</sup> Add "-T" for Tape and Reel.

# What's Inside

This Evaluation Board Kit contains the following materials:

- Qty(1) ISL6253EVAL1B Evaluation Board

- Qty(1) ISL6253EVAL1B Setup Procedure

# What is Needed

The following materials are recommended to perform testing:

- One adjustable 25V 6A power supply

- Two adjustable 6A constant current electronic loads

- Two DVMs

- One 500MHz four channel oscilloscope

- · Four passive oscilloscope voltage probes

- Two 10ADC Current Probes

- One Signal generator

# Jumper Selection Guide

### Step 1: Select the Number of Cells (Table 1)

The CELLS pin chooses the correct output voltage clamp for a given number of cells series-connected in the battery pack. Select the output voltage by placing a shunt jumper across the appropriate pins of JP1.

| SHUNT<br>JUMPER<br>LOCATION | CELLS PIN<br>CONNECTED<br>TO: | NUMBER OF<br>CELLS<br>CONNECTED<br>IN SERIES | 100%<br>CONSTANT<br>OUTPUT<br>VOLTAGE |

|-----------------------------|-------------------------------|----------------------------------------------|---------------------------------------|

| 1-2                         | VDD                           | 4                                            | 16.8                                  |

| 2-3                         | GND                           | 3                                            | 12.6                                  |

| Removed                     | Floating                      | 2                                            | 8.4                                   |

#### TABLE 1. JUMPER JP1 FUNCTIONS

### Step 2: Select the Cell Trim Voltage (Table 2)

The VADJ pin trims the battery charger output voltage limit. Preset battery charger output voltage limits are selected by placing a shunt jumper across the appropriate pins of JP6. For other battery charger output voltage limits install a shunt jumper across pins 3 and 4 which connects the wiper of potentiometer R24 to VADJ. Potentiometer R24 may be removed and replaced with resistors R19 and R21. Resistor R20 limits the trim increase to 1%. Shorting R20 allows the trim to increase 5%. Decreasing trim range is unaffected.

| TABLE 2. | JUMPER JP6 FUNCTIONS |

|----------|----------------------|

|          |                      |

| SHUNT<br>LOCATION | VADJ<br>PIN                            | BATTERY<br>VOLTAGE CHANGE<br>PER CELL |  |

|-------------------|----------------------------------------|---------------------------------------|--|

| 1 to 3            | Through R20 to VREF                    | +1%                                   |  |

| 3 to 5            | To GND                                 | -5%                                   |  |

| 5 to 6            | Floating None                          |                                       |  |

| 3 to 4            | Through R20 To R24 Wiper<br>or R19/R21 | Adjustable between -<br>5% to +1%     |  |

The CHLIM pin chooses the desired battery charger current limit threshold. Preset battery charger current limit thresholds are selected by placing a shunt jumper across the appropriate pins of JP4. For other battery charger current limit thresholds install a shunt jumper across pins 3 and 4 which connects the wiper of potentiometer R22 to CHLIM. Potentiometer R22 may be removed and replaced with resistors R6 and R7.

| SHUNT<br>JUMPER<br>LOCATION | CHLIM PIN<br>CONNECTED<br>TO: | 100% CURRENT<br>FEEDBACK<br>CSOP TO CSON | 100%<br>CONSTANT<br>CURRENT |  |

|-----------------------------|-------------------------------|------------------------------------------|-----------------------------|--|

| Removed                     | 3.3V@TP10                     | 127mV                                    | 5.08A                       |  |

| 1-3                         | VREF                          | 100mV                                    | 4.00A                       |  |

| Removed                     | Floating                      | 65mV                                     | 2.60A                       |  |

| 3-5                         | GND                           | 30mV                                     | 1.20A                       |  |

| 3-4                         | R22 or R6/R7                  | 30mV to 127mV                            | 1.20A to 5.08A              |  |

TABLE 3. JUMPER JP4 FUNCTIONS

### Step 4: Select the AC Adapter Current Limit (Table 4)

The ACLIM pin chooses the desired AC adapter current limit threshold. Preset AC adapter current limit thresholds are selected by placing a shunt jumper across the appropriate pins of JP5. For other AC adapter current limit thresholds install a shunt jumper across pins 3 and 4 which connects the wiper of potentiometer R23 to ACLIM. Potentiometer R23 may be removed and replaced with resistors R17 and R18.

| TABLE 4. | JUMPER JP5 | FUNCTIONS |

|----------|------------|-----------|

|          |            |           |

| SHUNT<br>JUMPER<br>LOCATION | ACLIM PIN<br>CONNECTED<br>TO: | 100% CURRENT<br>FEEDBACK<br>CSIP TO CSIN | 100%<br>ADAPTER<br>CURRENT |  |

|-----------------------------|-------------------------------|------------------------------------------|----------------------------|--|

| 1-3                         | VREF                          | 103mV                                    | 5.15A                      |  |

| Removed                     | Floating                      | 78mV                                     | 3.90A                      |  |

| 3-5                         | GND                           | 53mV                                     | 2.65A                      |  |

| 3-4                         | R23 or R17/R18                | 53mV to 103mV                            | 2.65A to<br>5.15A          |  |

### Interface Connections

The input power source connects to header H1. Positive input power "+" connects to H1 pin 1, "+" SNS (if used) connects to H1 pin 2, "-" SNS (if used) connects to H1 pin 3, and "-" input power connects to H1 pin 4. The battery charger output connects to header H3. Positive battery charger output "+" connects to H3 pin 1, "+" SNS (if used) connects to H3 pin 2, "-" SNS (if used) connects to H3 pin 3, and "-" battery charger output connects to H3 pin 4. The system output connects to H2 pin 1, "+" SNS (if used) connects to H2 pin 2, "-" SNS (if used) connects to H3 pin 4. The system output connects to H2 pin 1, "+" SNS (if used) connects to H2 pin 2, "-" SNS (if used) connects to H2 pin 3, and "-" system output connects to H2 pin 4.

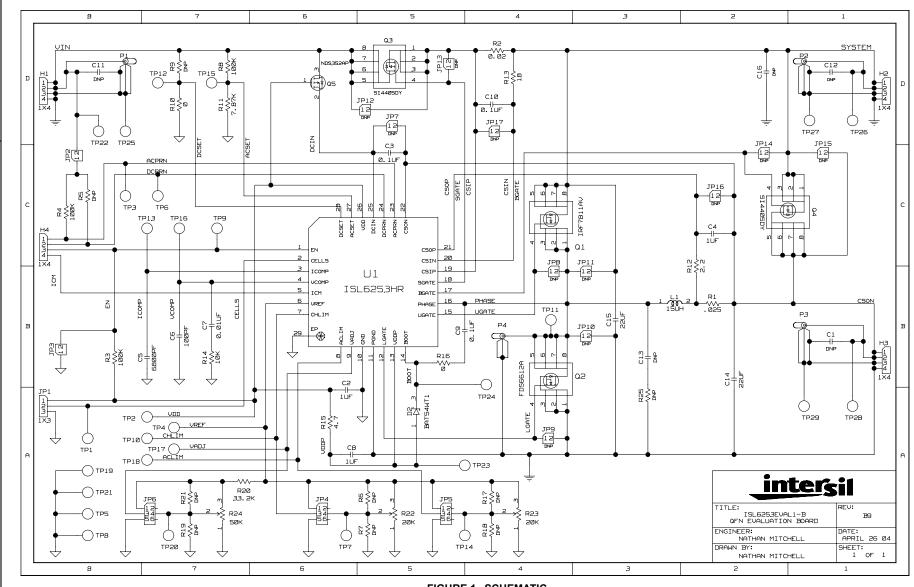

**FIGURE 1. SCHEMATIC**

intersil

ω

| QTY | REF DES     | DESCRIPTION                                    | MFG NAME  | PART NUMBER           |

|-----|-------------|------------------------------------------------|-----------|-----------------------|

| 1   | C6          | Capacitor, SMD, 0603, 100pF, 50V, 5%, COG      | TDK       | C1608COG1H101J        |

| 1   | C7          | Capacitor, SMD, 0805, 0.01µF, 50V, 5%, COG     | TDK       | C2012COG1H103J        |

| 1   | C5          | Capacitor, SMD, 0805, 6800pF, 50V, 5%, COG     | TDK       | C2012COG1H682J        |

| 3   | C2, C4, C8  | Capacitor, SMD, 0805, 1.0µF, 16V, 20%, X7R     | TDK       | C2012X7R1C105M        |

| 3   | C3, C9, C10 | Capacitor, SMD, 0805, 0.1µF, 50V, 10%, X7R     | TDK       | C2012X7R1H104K        |

| 2   | C14, C15    | Capacitor, SMD, 1812, 22µF, 25V, 20%, X5R      | TDK       | C4532X5R1E226M        |

| 1   | L1          | Choke, SMD, 8mm, 15µH, 20%, 5.65A, Shielded    | Sumida    | CDRH127/LD-150NC      |

| 1   | U1          | IC, Battery Charger, 28P, QFN, -10°C to +100°C | Intersil  | ISL6253HR             |

| 1   | Q2          | MOSFET, N-CH, 8P, SOIC, 30V, 8.4A, 0.022Ω      | Fairchild | FDS6612A              |

| 1   | Q1          | MOSFET, N-CH, 8P, SOIC, 30V, 10.8A, 0.011Ω     | IR        | IRF7811AV             |

| 1   | Q5          | MOSFET, P-CH, 3P, SOT23, -30V, -0.9A, 0.5Ω     | Fairchild | NDS352AP              |

| 2   | Q3, Q4      | MOSFET, P-CH, 8P, SOIC, -30V, -17A, 0.0075Ω    | Siliconix | SI4405DY              |

| 1   | R2          | Resistor, Shunt, SMD, 2010, 0.020Ω, 1W, 1%     | IRC       | LRC-LRF2010-01-R020-F |

| 1   | R1          | Resistor, Shunt, SMD, 2010, 0.025Ω, 1W, 1%     | IRC       | LRC-LRF2010-01-R025-F |

| 1   | R13         | Resistor, SMD, 0805, 18Ω, 0.125W, 5%           | KOA       | RK73B2AT180J          |

| 1   | R12         | Resistor, SMD, 0805, 2.2Ω, 0.125W, 5%          | KOA       | RK73B2AT2R2J          |

| 1   | R15         | Resistor, SMD, 0805, 4.7Ω, 0.125W, 5%          | KOA       | RK73B2AT4R7J          |

| 1   | R14         | Resistor, SMD, 0805, 10kΩ, 0.125W, 1%          | KOA       | RK73H2AT1002F         |

| 1   | R11         | Resistor, SMD, 0805, 7.87kΩ, 0.125W, 1%        | KOA       | RK73H2AT7871F         |

| 3   | R3, R4, R8  | Resistor, SMD, 0805, 100kΩ, 0.125W, 1%         | KOA       | RK73H2AT1003F         |

| 1   | R20         | Resistor, SMD, 0805, 33.2kΩ, 0.125W, 1%        | KOA       | RK73H2AT3322F         |

| 2   | R10, R16    | Resistor, SMD, 0805, 0Ω, 2A, 50mΩ Max          | KOA       | RK73Z2AT              |

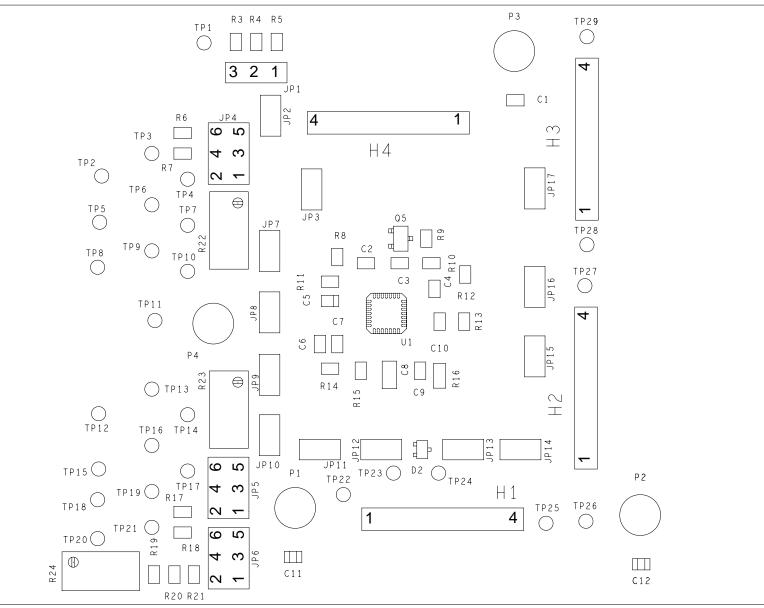

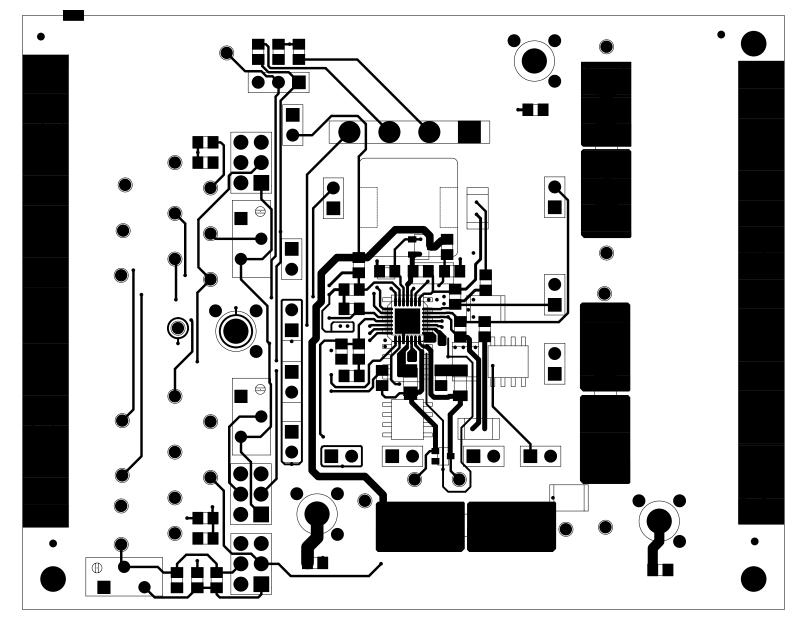

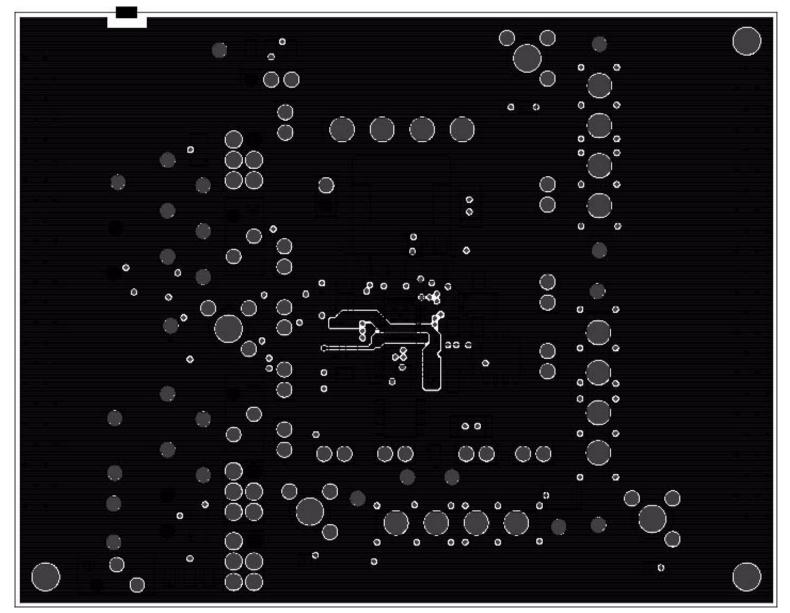

FIGURE 2. TOP SILK AND ASSEMBLY

Сı

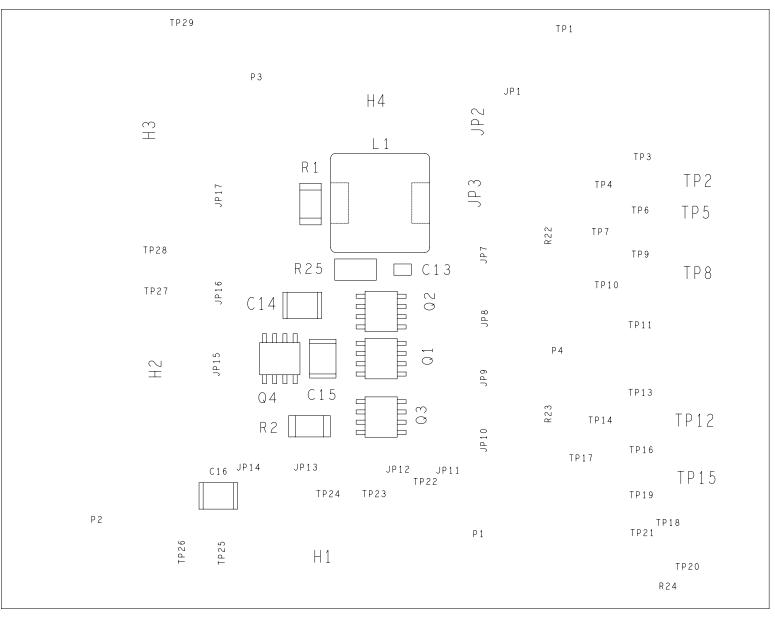

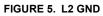

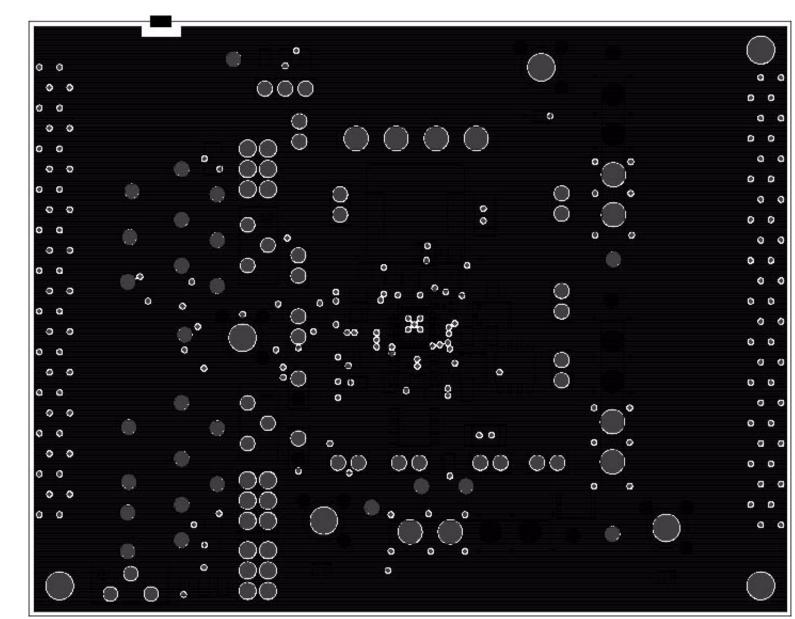

FIGURE 3. BOTTOM SILK AND ASSEMBLY

**Application Note 1061**

$\overline{\phantom{a}}$

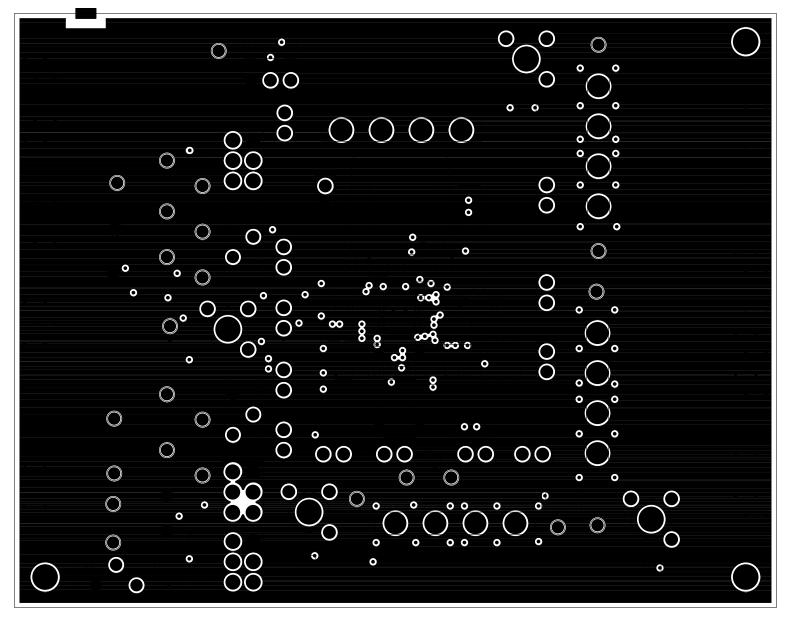

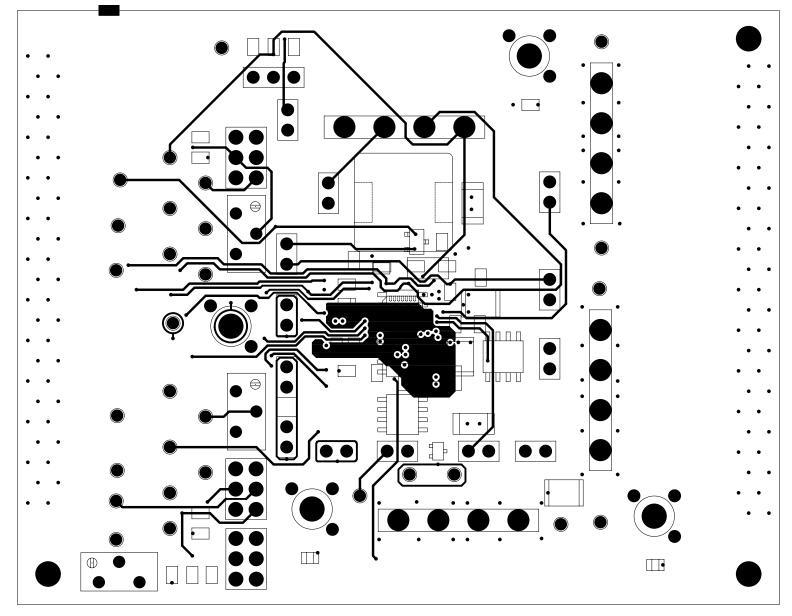

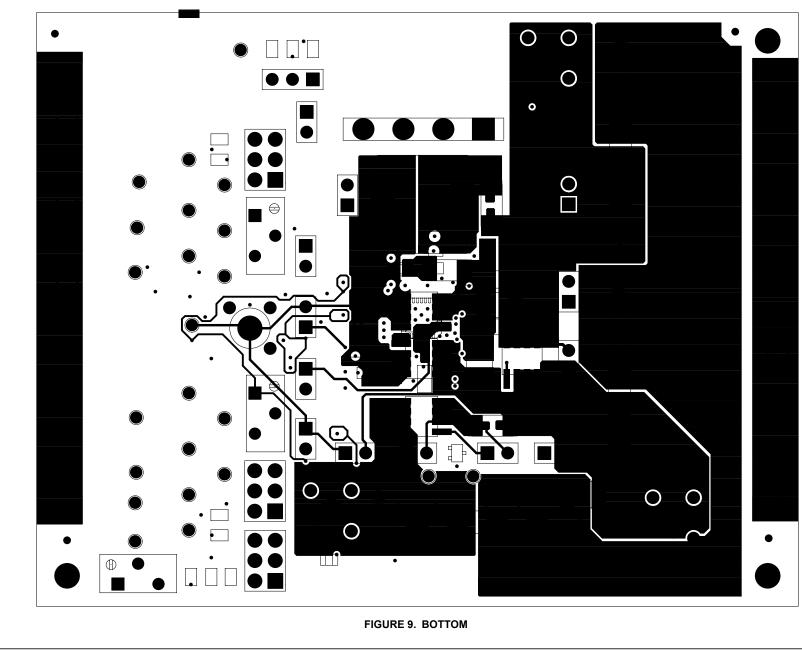

FIGURE 7. L4 GND

FIGURE 8. L5 GND

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com